FPGA(Verilog)实现uart传输协议传输数据(含仿真)

目录

实现功能:

1.接收uart串行数据,输出并行数据(1byte)。

2.输入并行数据(1byte),输出uart串行数据。

3.完成uart传输的1次环回。

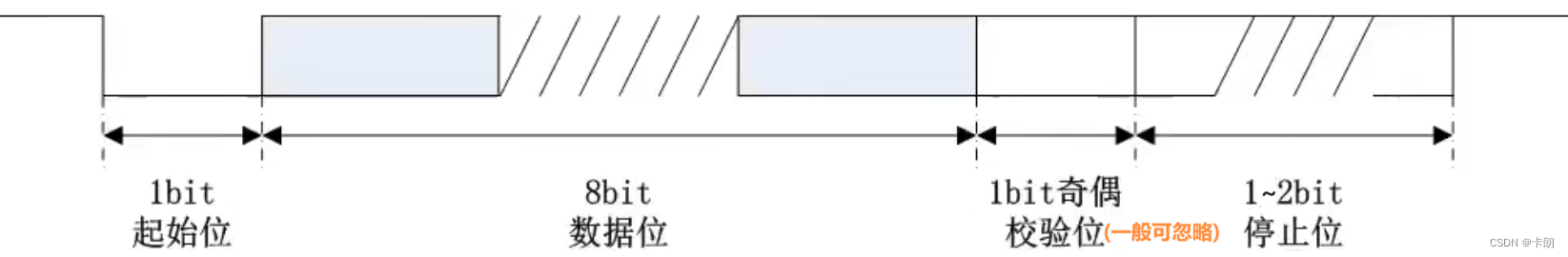

uart协议的1帧数据传输

模块封装-port设置

Verilog代码实现

1.uart接收模块:接收串行数据,输出并行数据和其有效标志。

仿真结果:

2.uart发送模块:接收并行数据,发送串行数据。

仿真结果:

3.uart环回测试。

仿真验证:

仿真结果:

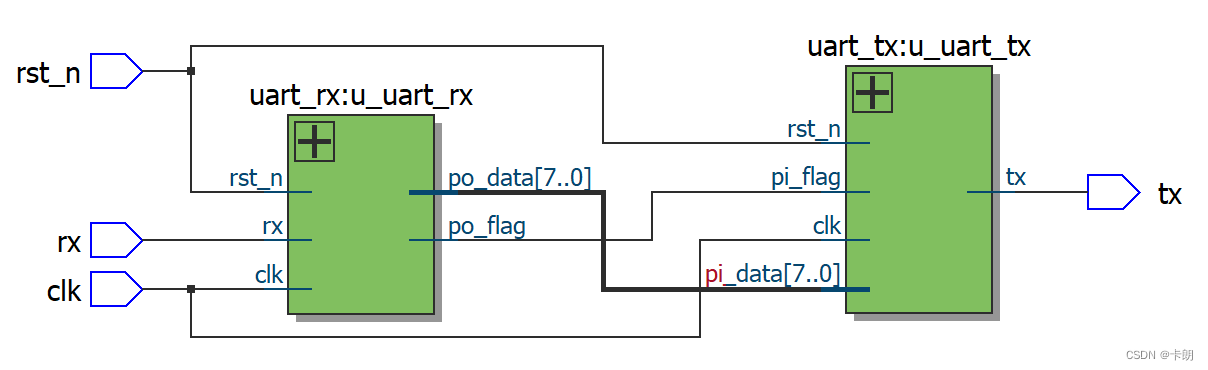

FPGA系统集成-RTL框图

实现功能:

1.接收uart串行数据,输出并行数据(1byte)。

2.输入并行数据(1byte),输出uart串行数据。

3.完成uart传输的1次环回。

uart协议的1帧数据传输

模块封装-port设置

Verilog代码实现

1.uart接收模块:接收串行数据,输出并行数据和其有效标志。

module uart_rx#( parameter UART_BPS='d9600 , //波特率:1s传输9600个bit parameter CLK_FREQ='d50_000_000 //时钟频率:50MHz )( input wire clk , input wire rst_n , input wire rx , //接收的串行数据 output reg [7:0] po_data , //输出并行数据 output reg po_flag //输出有效并行数据的标志信号 );

首先对rx进行时钟同步,消除亚稳态,以及打拍处理提取下降沿;

always@(posedge clk or negedge rst_n) if(!rst_n) begin rx_d1=4'd1) && (bit_cnt

文章版权声明:除非注明,否则均为主机测评原创文章,转载或复制请以超链接形式并注明出处。

还没有评论,来说两句吧...